差動増幅回路の入出力試験

差動増幅回路について

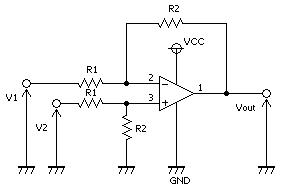

差動増幅回路の回路図

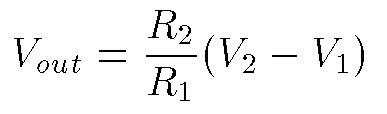

上図に差動増幅回路の回路図を示す。 差動増幅回路では、入力電圧Vinと出力電圧Voutの関係が 次式で表わされる。

LabVIEWの実験用プログラム

R1=10kΩ、R2=75kΩの場合のVinとVoutの関係を実験して調べる。 LabVIEWを用いて0~1.0Vまでの電圧をVinに出力し、VoutをVinを変える度に測定し、テキストデータとして出力するプログラムを作成した。プログラム→iotest.vi

実験条件

抵抗の実測値R1=10.01kΩ、10.01kΩ

R2=75.12kΩ、74.9kΩ

オペアンプへの供給電圧 7.30V

結果と考察

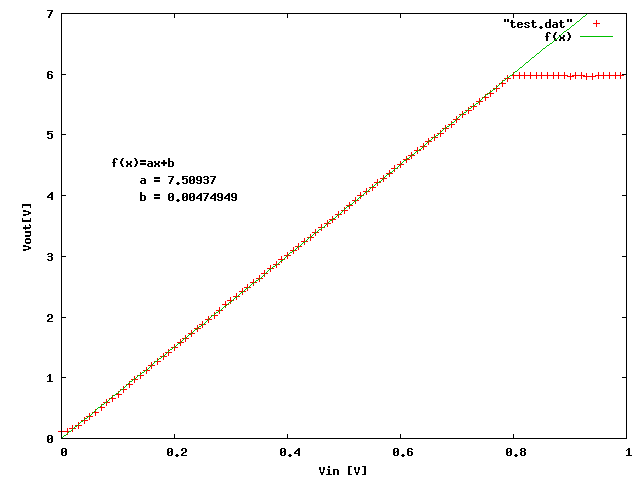

結果を下図に示す。

理論的には増幅率7.5の出力電圧が得られるはずである。

出力電圧は6Vほどで頭打ちとなった。

Vinが0~0.75Vの範囲ではVoutとVinは比例関係がある

とみられる。

図中の近似曲線は、Vinが0~0.75の範囲のデータを用いて最小二乗法で求めたものである。

直線の傾きから実際の増幅率は7.5と理論値とほとんど一致した。

差動増幅回路の入出力関係